# TSC701 the SPARC Communication Controller that breaks the limits of your Application

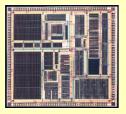

The TSC701 is a **32-bit Embedded SPARC Processor** especially designed for the Communication Market. Built around TEMIC's **SPARClet<sup>TM</sup> architecture**, the TSC701 provides a full one-chip system solution with a high performance core integrating **DSP and High Speed HDLC Controllers** and the necessary peripherals for this field of application.

### Performance

- 50 MIPS (@50MHz) SPARC V8 Compatible CPU

- High HDLC Processing Power: from **96** full duplex channels (worst case) up to **336 channels** (best case configuration).

- Up to **8 Mbps** Transmission Speed on each of the **4 HSSL** (High Speed Serial Line).

- **DSP** capability: one cycle efficient 32x32-bit multiplier.

# **Key Features**

- Communications Functions:

- ° Communication Coprocessor (CCP)

- 4 HSSL: asynchronous, synchronous (Point to Point and Multipoint) and PCM (T1, E1, T2... lines)

- DSP Capability:

- Fully Parallel On-Chip 32x32-bit Multiplier

- Integrated Instruction Cache (16 KB) and Data Cache (8 KB)

- Multiprocessing Capability.

| Clock & Reset        |               |                             |               |               |    |                               |            |  |

|----------------------|---------------|-----------------------------|---------------|---------------|----|-------------------------------|------------|--|

|                      |               |                             |               |               |    | -                             |            |  |

| Fetch & decode       | e Unit        | Power & clock<br>Management | ⇔             | PIA           | (- | ╞                             |            |  |

|                      |               |                             | ₿             | GP<br>Timer 1 | -  | -                             | s          |  |

|                      | OS L          | ₿                           | GP<br>Timer 2 | -             | ┢  | Synchronous Serial Interfaces |            |  |

| Instruction<br>cache | Data<br>cache |                             | ₿             | Watch<br>Dog  | -  | -                             | ous Seria  |  |

|                      |               | Timer 2                     | ₿             | HSSL1         | ┝  | ⇒                             | al Interfa |  |

| System Bus           |               |                             | ₿             | HSSL2         |    |                               | (Ces       |  |

| Bus Interface        | 1             |                             | ⇔             | HSSL3         |    |                               |            |  |

| Controller<br>(BIC)  | JTAG          | C701<br>Perlpherals         | ⇔             | HSSL4         | -  |                               |            |  |

|                      |               |                             | 7             |               | -  | J                             |            |  |

| Memory & IO Bus      | JTAG port     |                             | ▼             |               |    |                               |            |  |

| <b>Typical Applications</b>    | Main Benefits                                                             |

|--------------------------------|---------------------------------------------------------------------------|

| • Cellular Phone Base Stations | <ul><li>Integration of the DSP function</li><li>Multiprocessing</li></ul> |

| • ISDN Routers                 | • Meet today's and tomorrow's bit rates requirements                      |

| WAN Switching systems          | • Up to 336 HDLC channels                                                 |

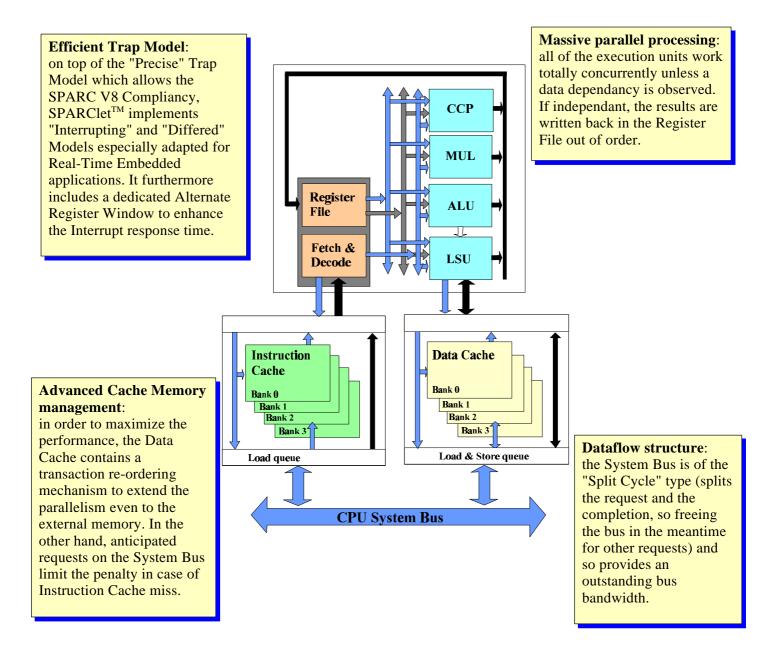

# About the SPARClet<sup>TM</sup> Architecture

SPARClet<sup>™</sup> Architecture has been developed by TEMIC and especially designed for the Embedded Market. Beside being fully SPARC V8 Compliant and so benefiting of the Tools running on Sun SPARCstations, SPARClet<sup>™</sup> provides extra features in the areas of real-time performance and on-chip DSP functions.

SPARClet<sup>™</sup> is based upon the following principles:

The SPARC V8 Instruction Set has been enriched with new instructions: SCAN (bit scanning), Shuffle (bit/nibble/byte/half-word swapping), and the instructions dedicated to the on-chip coprocessors (MUL and CCP for the TSC701).

# **Design your application around the TSC701**

In order to provide a comprehensive solution, a full range of software and debug tools has been developed around the TSC701.

## **Code Development Tools**

Although SPARClet<sup>TM</sup> is binary compatible with the widely spread SPARC V8 standard and as so can use any available compliant compiler, an optimized compiler is needed to take the architecture best benefits (parallel processing) and to use the additional instructions (SCAN, SHUFFLE and the specific internal co-processors instruction set).

The California based company CYGNUS, one of the compiler's market leaders, provides the SPARClet<sup>TM</sup> CDK (CYGNUS Development Kit) package which includes a GNU based C/C++ compiler and the RGDB remote debugger.

The CDK environment package is proposed for Sun OS, Solaris and Windows 3.1 platforms.

OFUS

## **Starter & Application Kits**

Those support kits available from TEMIC include:

- the TSC701 Demonstration Board (PCI, Ethernet)

- a debug monitor

- the necessary software libraries for:

- ° the on-chip peripherals and coprocessors

- the basic applicative functions (HDLC, Software DMA,...)

- the SPARClet<sup>TM</sup> CDK

## **Real-Time Operating System**

The two first Operating Systems ported to the SPARClet<sup>™</sup> architecture are:

- Chorus OS from Chorus Systems

- VxWorks/Tornado from Wind River Systems

## **Development and Debug Tools**

#### Architecture Simulator

The SASlet package provides an easy way to simulate and debug TSC701 code and to evaluate its performance prior to the availability of the hardware target.

#### Logic analyser

SPARClet<sup>TM</sup> dedicated tools including hardware probes and on-line disassembling are developed by Tektronics.

#### **ROM emulator**

TEMIC recommends XLNT ROM emulation equipments. **JTAG tool**

Will be available early 1997.

**Real-Time Trace and Performance monitoring** TEMIC recommends CodeTest from AMC

# **TSC701 Features**

## **CPU Core**

- V8 compliant SPARC Processor

- Little & Big Endian data organizations supported

- Multiply and Accumulate instructions

- Bit scanning and bit shuffling instructions

- 8 Register Windows (136 registers)

- Alternate Window Registers (32 registers)

- Communication Coprocessor (CCP) Coder/Decoder/CRC Supported protocols: HDLC,V.110, proprietary 100 Mbps max. @ 50MHz

- On-Chip Cache Memory

- Four ways associative

- Lockable by Bank

- Instruction Cache: 16 KBytes

- Data Cache: 8 KBytes

- System Bus

Split Cycle Bus connecting the Core and the **On-Chip Peripherals**

## **On-Chip Peripherals**

- Bus Interface Controller (BIC)

- 256 Mbytes address space

- DRAM / SRAM / ROM glueless interface

- Programmable Timings

- Multimaster bus support

- 8-bit boot feature

- Control signals generated for 48 Mbytes.

- JTAG Test Access Port

- Boundary Scan

- System Bus agents access for debug purpose

- Peripheral Interface Adapter (PIA)

- 10-bit bi-directional port

- Programmable Interrupt Level

- Serial Links

- 4 High Speed Serial Links (HSSL)

- support of asynchronous, synchronous (Point to Point and Multipoint) and PCM

- Timers

- 2 General Purpose Timers

- 2 Operating System Timers

- 1 Watchdog

### **Technology**

- Fully static CMOS Technology

- Temperature Range: 0 to 70°C

- Operating Frequency: 33MHz & 50MHz

- Packages: 225-pin BGA, 208-pin PQFP and 209-pin PGA

## **On-line support**

- SPARClet<sup>TM</sup> e-mail hot-line: sparclet@temic.fr

- ftp site: public.matramhs.fr

- (directory: /pub/pbomel-dad) • WWW

TEMIC: www.temic.de CYGNUS: www.cygnus.com Chorus Systems: www.chorus.com Wind River Systems: www.wrs.com SPARC International: www.sparc.com

### **Available Documentation**

- TSC701 User's Manual

- TSC701 Electrical & Mechanical Specification

- TSC701 Starter-Kit User's Guide

- SPARClet<sup>TM</sup> Brochure

- SPARClet<sup>TM</sup> CD ROM

for more information on our products:

for more information on our products: <u>TEMIC Semiconductors Sales offices</u>: <u>Europe</u>: France Tel: (33) 1 30 60 7000 Fax: (33) 1 30 60 7111 / Germany Tel: (49) 7131 67 0 Fax: (49) 7131 67 2100 / Italy Tel: (39) 2 332 12 332 Fax: (39) 2 332 12 234 / Spain Tel: (34) 1 564 5181 Fax: (34) 1 562 7514 / Scandinavia Tel: (46) 8 733 0090 Fax: (46) 8 733 0558 / United Kingdom Tel: (44) 1 344 70 73 00 Fax: (44) 1 344 42 73 71 **North America:** Central Tel.: (810) 244 061 0 Fax.: (810) 244 08 48 / Eastern Tel.: (908) 735 61 00 Fax: (908) 735 22 58 / Western Tel.: (408) 970 57 00 Fax: (408) 970 39 50 / Mexico Tel.: (52) 5 564 92 76 Fax:: (52) 5 566 08 400 Japan : Tel.: (81) 35 562 33 21 Fax:: (81) 35 562 33 16

Asia : China Tel.: (86) 21 5677 5946 Fax.: (86) 21 5677 3403 / Hong Kong Tel.: (852) 2 37 89 789 Fax.: (852) 2 37 55 733 / Korea Tel.: (822) 785 1136 Fax.: (822) 785 1137 / Singapore Tel.: (65) 788 668 Fax.: (65) 788 00 31 / Taiwan Tel.: (886) 2 755 51 08 Fax.: (886) 2 755 47 77

TEMIC Semiconductors World Wide Web : http://www.temic.de